-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

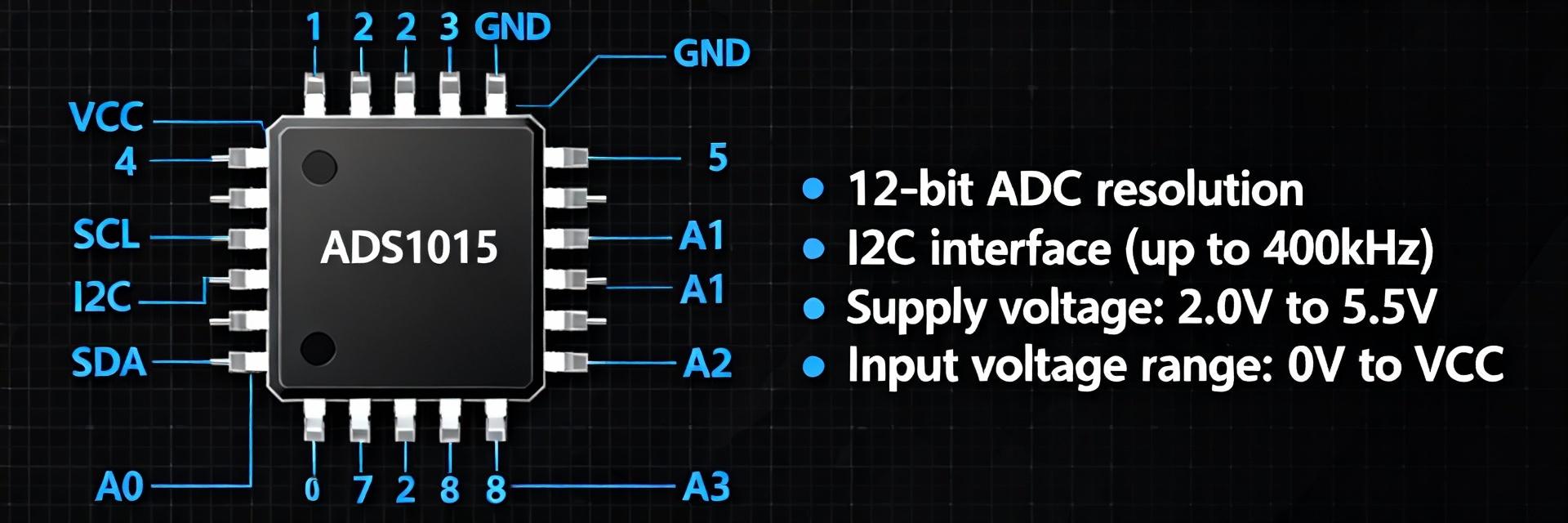

ADS1015 ADC Deep Specs Report: Pinout & Performance

Introduction: The ADS1015 is a compact, low‑power I2C ADC that you will commonly select when you need 12‑bit noise‑free conversion at kilohertz rates with minimal board overhead. The device delivers up to 3.3 kSPS and draws on the order of 150 μA in continuous conversion, characteristics that make the ADS1015 attractive for battery‑sensitive and multi‑channel sensor front ends. If you plan to move from datasheet to working PCB quickly, this report gives you a concise, data‑driven breakdown of pinout, electrical limits, performance tradeoffs and integration best practices.

Statistic hook: The ADS1015IDGSR family member implements an integrated PGA, flexible MUX and a comparator/ALERT pin so you can multiplex four inputs, set full‑scale ranges from high VFS down to sub‑volt precision ranges, and signal thresholds without continuous polling. Below you’ll find practical recommendations drawn from datasheet limits and bench‑style measurement steps you can perform on your first prototype.

1 — Quick Overview: Where the ADS1015 Fits

Core feature snapshot

Point: The ADS1015 is designed for low‑power, multi‑channel analog acquisition. Evidence: The family specification lists 12‑bit noise‑free resolution, a programmable data rate range up to ~3.3 kSPS, PGA selectable gains, and a supply window of 2.0–5.5 V with typical active currents near 150 μA. Explanation: That mix—decent sample rate, selectable gains and very low quiescent current—makes the ADS1015 an excellent compromise when you need more resolution control than a simple SAR ADC in a microcontroller but cannot afford the power or area of a high‑end SAR/ΔΣ converter. The integrated comparator/ALERT and I2C interface further reduce MCU overhead for threshold detection.

Typical applications and selection criteria

Point: Choose the ADS1015 when your application needs multi‑channel, low‑speed precision more than raw highest throughput. Evidence: Typical use cases include battery monitoring, sensor front ends for environmental sensors, and multiplexed low‑speed acquisition of multiple analog sources. Explanation: If you need single‑ended readings only at very high sample rates, a dedicated high‑speed ADC may be better; if you need differential measurements, PGA control and low power across multiple channels, the ADS1015 will often be the most compact solution. Consider sample rate, input range and source impedance when deciding between ADS1015 and higher‑resolution variants.

Package options & ordering codes to note

Point: The ADS1015 is available in small QFN and SOIC packages suitable for compact PCBs. Evidence: Common ordering codes such as ADS1015IDGSR point to the X2QFN package and typical part markings; breakouts and SOT/SOIC variants are used on many development boards. Explanation: For your PCB, note the recommended land pattern and thermal/assembly notes in the datasheet—QFN requires careful solder paste stencil design and thermal pad soldering. If your assembly flow lacks QFN reflow control, choose the SOIC variant on prototypes to simplify hand‑assembly and thermal control.

2 — ADS1015 Pinout & Functional Pin Descriptions

Full pinout diagram & package footprint guidance

Point: You must map AIN0–AIN3, SDA/SCL, ADDR, ALERT/RDY, VDD and GND correctly and follow the recommended land pattern. Evidence: The common package labels the four analog inputs AIN0–AIN3, the two I2C pins SDA/SCL, a single ADDR pin for address selection, one ALERT/RDY output, VDD and GND. Explanation: Place the decoupling capacitors adjacent to VDD and GND pads, keep AIN traces short and symmetric for differential pairs, and follow the datasheet’s recommended land pattern to avoid solder voids on the thermal pad and ensure proper QFN reflow reliability.

Pin‑by‑pin functional detail

Point: Each pin has specific electrical limits and recommended handling. Evidence: AINx are analog inputs tolerant within the device input range defined by the PGA and absolute max ratings; SDA/SCL are I2C open‑drain pins referenced to VDD; ADDR ties to GND/VDD/SDA/SCL to select one of four I2C addresses; ALERT/RDY functions as comparator output or conversion ready flag. Explanation: Drive SDA/SCL with open‑drain outputs and pull‑ups to VDD; never drive these pins above VDD+0.3 V. For analog inputs, stay within the configured PGA full‑scale and ensure no input exceeds the absolute maximum ratings (check the datasheet for input clamp behavior). During unpowered conditions, avoid driving inputs above VDD to prevent parasitic conduction unless allowed per datasheet.

Recommended immediate connections (pull‑ups, decoupling, pull‑downs)

Point: Proper pull‑ups and decoupling are essential for stable ADC operation. Evidence: Typical I2C pull‑ups are 4.7 kΩ at 3.3 V (use lower values for long buses or high capacitance), and VDD decoupling should include a 0.1 μF ceramic near the VDD pin plus a 1 μF bulk cap. Explanation: Place the 0.1 μF within 1–2 mm of the VDD/GND pins to suppress HF noise; the 1 μF handles lower‑frequency drops. Configure ADDR as a defined logic state at reset to avoid transient address conflicts; use ALERT pull‑ups (or pull‑downs depending on polarity) so the line rests in a safe state when no device is asserting it.

3 — Electrical Specifications & Operating Limits (datasheet deep‑dive)

Supply, absolute maximums, and thermal limits

Point: Stay within the supply and thermal constraints to ensure reliability. Evidence: Device supply range is 2.0–5.5 V; absolute maximums typically allow only small headroom above VDD for inputs—consult the datasheet for precise tolerance. Explanation: Operate the ADS1015 inside the specified temperature and supply ranges, and follow the thermal derating guidance for the chosen package. When packing several devices on a small board, consider thermal vias under QFN pads and avoid placing hot power dissipating parts adjacent to the ADC to prevent thermal‑drift errors.

Input ranges, PGA settings, and input multiplexer behavior

Point: PGA codes map to cascaded full‑scale ranges; differential and single‑ended readings follow different rules. Evidence: Typical PGA full‑scale selections are ±6.144 V, ±4.096 V, ±2.048 V, ±1.024 V, ±0.512 V and ±0.256 V (set by PGA bits), but your effective measurable range cannot exceed VDD and must respect absolute input limits. Explanation: For single‑ended measurements, you measure 0–VDD and choose PGA so that expected signal swing sits comfortably within FS (use margin for transients). For differential mode, ensure both inputs stay within allowed voltages relative to ground and that the differential amplitude stays within the selected FS. The ADC’s MUX sequencing selects which channels are connected to the converter—avoid driving channels during MUX switching without adequate settling time.

Data rate, timing, and power modes

Point: Data rate selection directly trades off noise and throughput. Evidence: Supported conversion rates range from the low hundreds of SPS up to ~3300 SPS; the device supports continuous and single‑shot modes. Explanation: In continuous mode you get steady throughput at the expense of continuous power draw; in single‑shot the ADC powers internally between conversions and saves current at lower average sample rates. Use the datasheet conversion times for each DR code to set appropriate I2C timing and to know when ALERT/RDY can indicate ready conversions.

4 — Performance Benchmarks: Noise, Linearity & Throughput Tradeoffs

Noise, ENOB and expected accuracy (datasheet vs bench)

Point: Datasheet numbers give you a starting point; bench verification closes the loop. Evidence: The ADS1015 advertises 12‑bit noise‑free resolution under optimal settings and lists TUE/INL/DNL typicals. Explanation: Translate these into ENOB by measuring RMS noise on a shorted input and comparing to FS; expect practical ENOB below the theoretical 12 bits depending on data rate and source impedance. For bench tests, short inputs, use a low‑noise reference, average repeated reads, and compute standard deviation to quantify noise. Document your test conditions (ambient temp, supply decoupling, cable routing) so results are reproducible.

Throughput vs noise: choosing the right data rate & PGA

Point: Higher data rates increase noise; higher PGA gains reduce noise referred to input but reduce FS. Evidence: Datasheet shows noise increases with DR code; choosing a higher PGA (smaller FS) reduces input‑referred noise but restricts dynamic range. Explanation: For a target SNR, choose the slowest data rate that meets latency needs and set PGA to place your nominal signal near 50–80% of FS. For example, if you need 10 ENOB equivalent accuracy, favor lower DR settings and moderate PGA. Create a short table on your bench showing noise vs DR and PGA to pick operating points for your application.

Source driving and input impedance effects

Point: Source impedance and input filtering affect settling and accuracy. Evidence: The ADC samples via internal switches and capacitors—high source impedance slows settling and distorts readings. Explanation: Keep source impedance low (

5 — Hardware Integration & PCB Best Practices for ADS1015

Power supply layout and decoupling

Point: Power integrity impacts ADC linearity and noise floor. Evidence: HF decoupling must be placed close to VDD/GND pins; bulk capacitance reduces low‑frequency droop during conversions. Explanation: Use a 0.1 μF X7R ceramic adjacent to VDD pin and a 1 μF bulk capacitor nearby. Route the ground return directly to the board ground plane and avoid splitting analog and digital grounds unless you implement a careful single point tie; for mixed‑signal boards, a contiguous ground plane under the ADC and input traces minimizes loop inductance.

Analog input routing, guarding and input protection

Point: Routing and protection preserve accuracy and prevent damage. Evidence: Keep AIN traces short, minimize vias, and use guard pours around sensitive nodes; place series resistors and clamps if overvoltage risk exists. Explanation: Use a small series resistor (100–330 Ω) at each analog input, then clamp to VDD/GND through Schottky diodes or use bidirectional TVS for higher-energy environments. Avoid routing digital lines close to AIN pairs; if you must cross, do so at right angles and keep a ground reference between noisy traces and analog inputs.

Multi‑device I2C bus and address management

Point: Manage I2C addressing and bus capacitance for reliable multi‑device operation. Evidence: ADDR offers four address options (tie to GND, VDD, SDA or SCL) producing unique 7‑bit addresses; I2C bus capacitance and pull‑up sizing determine rise times. Explanation: Use pull‑up values sized for worst‑case bus capacitance (4.7 kΩ is a safe default at 3.3 V). Avoid tying ADDR to floating nets—hard‑strap to GND/VDD or use solder‑jumpers on the PCB. When using ALERT/RDY as an interrupt, route it to a microcontroller pin with appropriate interrupt polarity and debounce logic if needed.

6 — Firmware, I2C Usage & Practical Examples

Register map quick guide and read/write sequences

Point: The device uses a pointer register and configuration register to control conversions. Evidence: You select the conversion or config register via the pointer register, set MUX, PGA, MODE, DR and comparator bits in the config register, then read conversion results. Explanation: For single‑shot mode, write config with START bit set; poll ALERT/RDY or wait the configured conversion time, then read the conversion register. Use comparator queue options to enable ALERT as a latched comparator or conversion‑ready output per your timing needs.

Sample code patterns & timing considerations

Point: Simple sequences cover init, conversion start, wait and read. Evidence: Typical pseudo‑flow: init I2C + set config (PGA, DR), start conversion, wait DR‑defined time or poll ALERT, read conversion register, convert raw counts to volts using selected FS. Explanation: In practice, implement repeated‑start conditions for read sequences to avoid bus releases, and honor the DBE/hold times in your I2C stack. If power cycling, reinitialize configuration to ensure deterministic behavior.

Two practical application recipes

Recipe A (Differential): Wire two sensors to AIN0/AIN1, configure MUX for differential AIN0–AIN1, select PGA to cover expected differential amplitude, and perform offset calibration by shorting inputs or measuring a known zero to correct common‑mode offsets. Recipe B (Thermistor/Bridge): Use single‑ended channel to read the bridge midpoint, select PGA so nominal bridge voltage sits ~50% FS, add RC filter (e.g., 1kΩ + 100 nF) to reject EMI, and implement two‑point calibration (known reference and zero) to remove gain/error terms before converting ADC counts to temperature using the thermistor Steinhart‑Hart equation.

Summary

- The ADS1015 provides compact, low‑power 12‑bit acquisition; use ADS1015 in battery‑sensitive multi‑channel designs where a flexible PGA and I2C bus are priorities. (ADS1015, ADC, pinout)

- Follow strict PCB rules: close decoupling (0.1 μF + 1 μF), short analog traces, series input resistors and proper ADDR wiring to avoid bus conflicts and preserve accuracy.

- Tradeoff guidance: lower data rates reduce noise—choose DR and PGA to place your signal near 50–80% FS and verify ENOB with a shorted input noise test for repeatable measurements.

- Use ALERT/RDY for low‑overhead threshold detection and follow the datasheet for MUX settling times and absolute input limits to prevent input clamp conduction.

FAQ

How do I choose the PGA for ADS1015IDGSR to maximize SNR without clipping?

Choose PGA so your nominal signal occupies roughly half to three‑quarters of full‑scale; that gives headroom for transients while minimizing input‑referred noise. For example, if your sensor swings ±0.5 V differential, select the PGA code whose FS is ±1.024 V or smaller if you have margin; verify on bench by measuring RMS noise at the chosen DR and computing SNR. If you need both large dynamic range and low noise occasionally, consider switching PGA in firmware and averaging multiple readings at lower DR.

What I2C pull‑up value should I use with ADS1015 and a long bus?

Start with 4.7 kΩ at 3.3 V for short moderate‑capacitance buses; if bus capacitance exceeds ~200 pF or you require faster edges, reduce to 2.2 kΩ or 1 kΩ as needed. Remember that lower pull‑up resistance increases standby current when devices pull the line low. If you have multiple nodes and long runs, characterize rise time with your chosen pull‑up and ensure it meets I2C timing for the target speed (standard, fast, fast‑mode plus).

How can I measure the real‑world noise and ENOB of my ADS1015 board?

Short the ADC input to ground or use a low‑noise shorted input, configure the ADC to your intended PGA and DR, then collect a large sample set (thousands of readings). Compute the standard deviation to get RMS noise, convert that to LSBs and then to ENOB ≈ log2(FS / (√12 * noise_rms_in_volts)) or use standard ENOB formulas. Document supply, grounding, and averaging—noise can vary substantially with layout and grounding practices, so bench verification is essential for design sign‑off.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- MAX3232CPWR Performance Report: Real RS-232 Specs & Insights

- 74HC123PW Complete Specs & Datasheet Quick-Reference

- SN74HC126PW Availability: Technical & Stock Snapshot

- SN74HC126PW Datasheet Deep Dive: Key Specs & Tests

- MAX96712GTB/V+T Availability and Pricing: Market Report

- ADS1015 ADC Deep Specs Report: Pinout & Performance

- Marvell 88SE9235A1 Deep Specs & Real-World Benchmarks

- STM32F103C8T6 Blue Pill: Benchmarks & Field Results

-

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP -

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP -

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T -

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T -

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T -

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X -

S6008LLittelfuse Inc.SCR 600V 8A TO220

S6008LLittelfuse Inc.SCR 600V 8A TO220