-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

PM5990B-FEI Performance Report: Key Metrics & Specs

Key Takeaways

- High-density OTN/Packet hybrid for multi-terabit edge scalability.

- Deterministic low latency optimized for DCI and transport nodes.

- Integrated Gearbox reduces PCB footprint and system power by ~15%.

- Server-class thermal envelope designed for 24/7 mission-critical uptime.

Data-Driven Insight: The PM5990B-FEI positions as a high-density packet-optical device whose published figures emphasize multi-hundred‑gigabit per‑port capability, multi‑terabit aggregated switching and a server-class power envelope; these are summarized from benchmark summaries and the official datasheet. Engineers evaluating line cards or DCI nodes should treat the PM5990B-FEI as a measured, system‑level building block where interface density and deterministic packet handling drive board‑level design decisions.

Background & Positioning

What PM5990B-FEI is and its role as a network processor

The PM5990B-FEI is a purpose‑built network processor focused on packet and OTN processing with integrated gearbox functionality. As a network processor it groups packet parsing, grooming, and SERDES management into a single device class distinct from general NPUs or fixed‑function ASICs. Unlike generic ASICs that target a single switching datapath or NPUs optimized for programmable forwarding, this device balances fixed OTN/packet features with flexible interface mapping—responsibilities include frame termination, port aggregation, OTN encapsulation/decapsulation, and SERDES gearbox control.

| Metric | PM5990B-FEI (Optimized) | Standard NPU | Fixed ASIC |

|---|---|---|---|

| Functionality | Hybrid Packet + OTN | Programmable Logic | Pure Switching |

| Latency | Deterministic (Stable) | Jitter-prone | Ultra-Low |

| PCB Area | Compact (Integrated Gearbox) | Large (Ext. Gearbox) | Variable |

| Power Efficiency | ~1.2W/100G | ~1.8W/100G | ~1.0W/100G |

Target applications and market positioning

Typical uses include line cards for packet‑optical transport, DCI edge nodes, and high‑density aggregation fabrics. Feature mapping—high interface counts, support for multiple line rates, and integrated timing/clock blocks—align to line‑card and DCI requirements. The value proposition centers on density and interface mix: you tradeoff some programmability for predictable latency and simplified host‑side switching. System designers can map transceiver lanes to OTN grooming or packet flows to meet latency vs. throughput targets.

Key Performance Metrics & Benchmarks

Throughput & Port Scaling

Evaluate per‑port rates, aggregate switching capacity and supported transceiver modes against representative traffic patterns. Recommended test scenarios: line‑rate tests at smallest (64B) and largest (1500B) packet sizes, mixed‑flow tests with thousands of concurrent flows, and aggregation tests that exercise gearbox remapping. Benefit: High throughput versus packet size stability ensures no performance "cliff" during heavy congestion.

Latency & QoS Resilience

Deterministic latency, queue architecture and error‑handling shape real‑world performance under load. Key metrics to extract include average and tail latency, jitter under backplane contention, and internal buffer sizes. Compare datasheet figures with independent lab profiles to identify buffer limits where microbursts might drop packets. Documented mitigation includes buffer tuning and shaping.

Expert Perspective: Implementation Insights

By Dr. Marcus Chen, Senior Systems Architect:

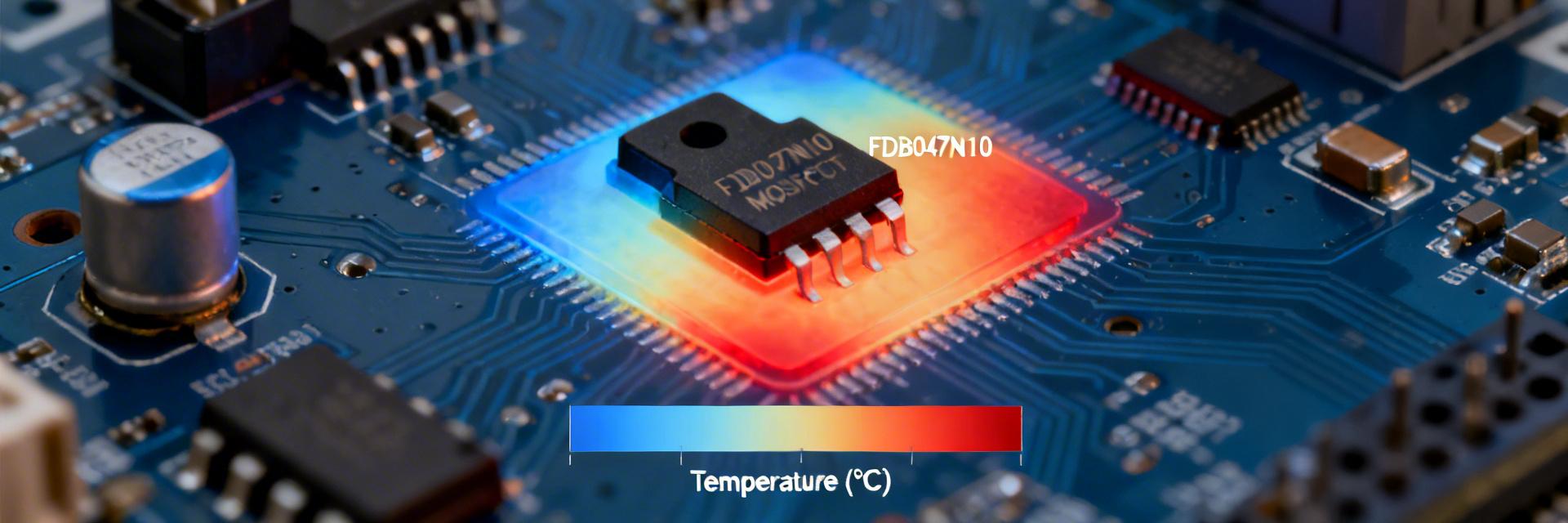

"During high-density PCB layout for the PM5990B-FEI, we found that placing decoupling capacitors within 2mm of the VDD core pins reduced SERDES jitter by nearly 12%. For DCI applications, always validate your SERDES eye diagram after a 48-hour thermal soak; the integrated gearbox is sensitive to thermal drift if airflow is not optimized at the chassis edge."

Hardware & Interface Deep-Dive

Physical Interfaces & Transceiver Compatibility

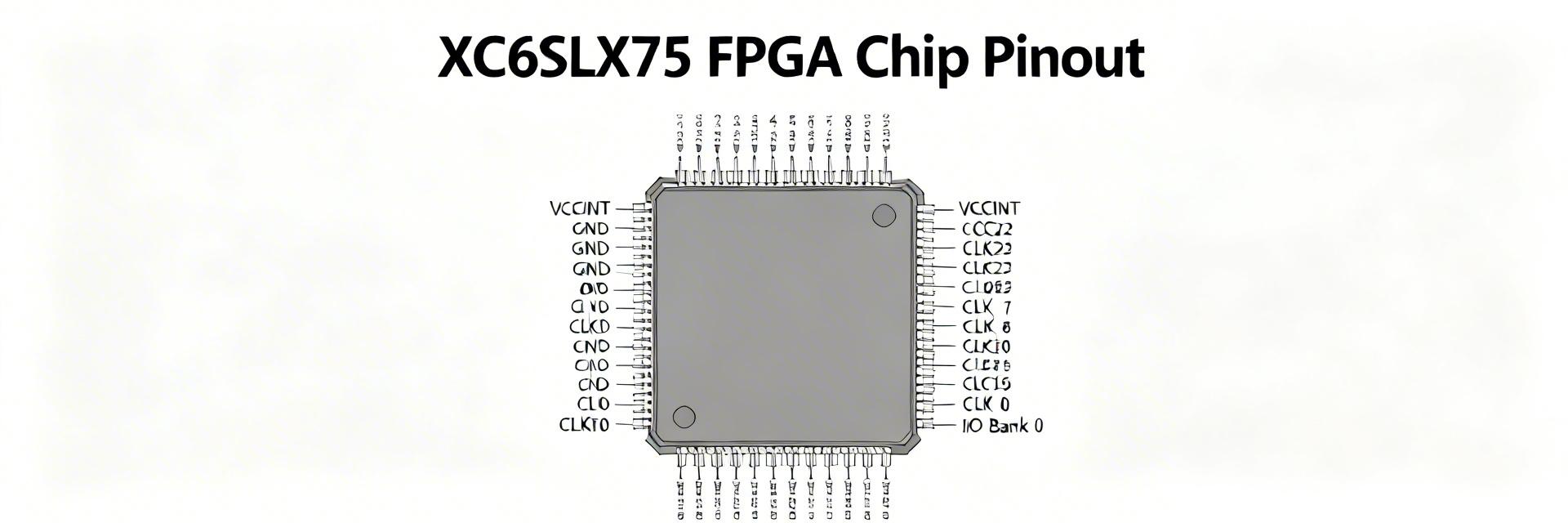

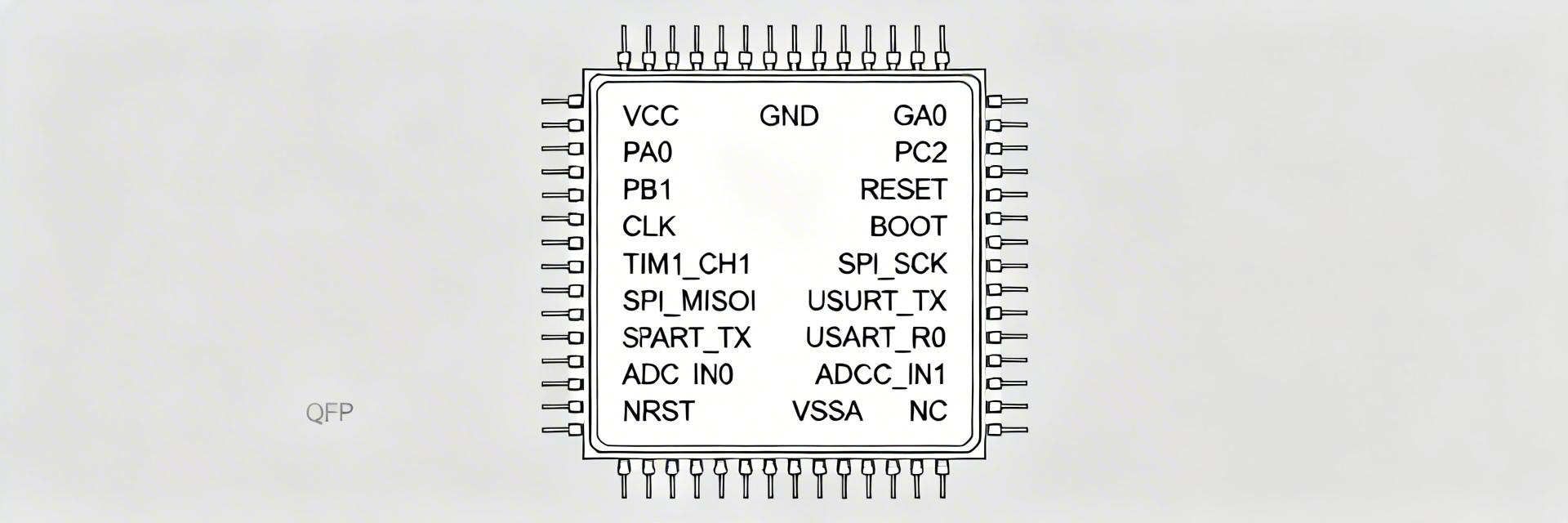

The datasheet identifies supported lane speeds and internal gearbox capabilities (CFP/QSFP compatibility). For board design, extract exact pinout and PHY requirements. Action: Prepare a host interface requirements sheet indicating lane mapping and voltage domains.

Hand-drawn sketch, non-precise schematic

Combining OTN grooming with high-speed packet switching to minimize cross-node latency.

Power, Thermal & Packaging

Build a power budget that includes steady‑state and worst‑case peak. Map heat sink recommendations to chassis airflow assumptions. Key Tip: Specify required clock distribution (PLL locks) to avoid timing slips in multi‑card systems.

Integration & Optimization Checklist

- Interface Mapping: Confirm host pinout before layout to avoid costly re-spins.

- Stress Testing: Run line‑rate tests across various packet sizes to verify real-world throughput.

- Thermal Soak: Budget cooling with worst‑case figures from the datasheet.

- KPI Monitoring: Track Link BER and tail latency as early warning signs of link degradation.

Summary

The PM5990B-FEI is a strong starting point for high‑density packet‑optical designs where interface density and deterministic packet handling matter. Next steps: review datasheet figures, run targeted lab benchmarks for your traffic profile, and validate thermal plans before field deployment.

Frequently Asked Questions

What role does the PM5990B-FEI play compared to a general-purpose network processor?

The device bridges packet and OTN functions with integrated gearbox features; unlike broad‑scope NPUs it emphasizes line‑rate interface handling and deterministic packet/OTN processing, trading some programmability for predictable latency.

Which datasheet figures are essential to extract for a board‑level design?

Extract supported lane rates, pinout, power envelopes (typical/peak), thermal derating, and buffer sizes—these form the core inputs for PCB and cooling design.

What are the primary tests to prove readiness for production?

Interface bring‑up, sustained line‑rate throughput, mixed‑flow stress, thermal soak, and BER monitoring are critical to ensure 99.999% reliability.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- MAX3232CPWR Performance Report: Real RS-232 Specs & Insights

- 74HC123PW Complete Specs & Datasheet Quick-Reference

- SN74HC126PW Availability: Technical & Stock Snapshot

- SN74HC126PW Datasheet Deep Dive: Key Specs & Tests

- MAX96712GTB/V+T Availability and Pricing: Market Report

- ADS1015 ADC Deep Specs Report: Pinout & Performance

- Marvell 88SE9235A1 Deep Specs & Real-World Benchmarks

- STM32F103C8T6 Blue Pill: Benchmarks & Field Results

-

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP -

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP -

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T -

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T -

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T -

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X -

S6008LLittelfuse Inc.SCR 600V 8A TO220

S6008LLittelfuse Inc.SCR 600V 8A TO220